2.2. Шини мікропроцесорної системи

Перш ніж переходити до особливостей циклів обміну, зупинимося докладніше на складі і призначенні різних шин мікропроцесорної системи.

Як вже згадувалося, в системну магістраль (системну шину) мікропроцесорної системи входить три основні інформаційні шини: адреси, даних і управління.

Шина даних - це основна шина, заради якої і створюється вся система. Кількість її розрядів (ліній зв'язку) визначає швидкість і ефективність інформаційного обміну, а також максимально можливу кількість команд.

Шина даних завжди двонаправлена, оскільки припускає передачу інформації в обох напрямах. Тип вихідного каскаду, що часто зустрічається, для ліній цієї шини - вихід з трьома станами.

Звичайно шина даних має 8, 16, 32 або 64 розряди. Зрозуміло, що за один цикл обміну по 64-розрядній шині може передаватися 8 байт інформації, а по 8-розрядній - тільки один байт. Розрядність шини даних визначає і розрядність всієї магістралі. Наприклад, коли говорять про 32-розрядну системну магістраль, мається на увазі, що вона має 32-розрядну шину даних.

Шина адреси - друга по важливості шина, яка визначає максимально можливу складність мікропроцесорної системи, тобто допустимий об'єм пам'яті і, отже, максимально можливий розмір програми і максимально можливий об'єм даних, що запам'ятовуються. Кількість адрес, забезпечуваних шиною адреси, визначається як 2N, де N - кількість розрядів. Наприклад, 16-розрядна шина адреси забезпечує 65 536 адрес. Розрядність шини адреси звичайно кратна 4 і може досягати 32 і навіть 64. Шина адреси може бути однонаправленою (коли магістраллю завжди управляє тільки процесор) або двонаправленою (коли процесор може тимчасово передавати управління магістраллю іншому пристрою, наприклад контроллеру ПДП). Найбільш часто використовуються типи вихідних каскадів з трьома станами або звичайні ТТЛ (з двома станами).

Як в шині даних, так і в шині адреси може використовуватися позитивна логіка або негативна логіка. При позитивній логіці високий рівень напруги відповідає логічній одиниці на відповідній лінії зв'язку, низький - логічному нулю. При негативній логіці - навпаки. В більшості випадків рівні сигналів на шинах - ТТЛ.

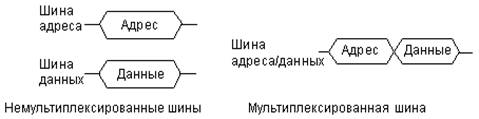

Для зниження загальної кількості ліній зв'язку магістралі часто застосовується мультиплексування шин адреси і даних. Тобто одні і ті ж лінії зв'язку використовуються в різні моменти часу для передачі як адреси, так і даних (на початку циклу - адреса, в кінці циклу - дані). Для фіксації цих моментів (стробує) служать спеціальні сигнали на шині управління. Зрозуміло, що мультиплексування шин адреси/данних забезпечує меншу швидкість обміну, вимагає більш тривалого циклу обміну (мал. 2.1). По типу шини адреси і шини даних всі магістралі також діляться на мультиплексовані і немультиплексовані .

Мал. 2.1. Мультиплексування шин адреси і даних.

В деяких мультиплексованих магістралях після одного коду адреси передається декілька кодів даних (масив даних). Це дозволяє істотно підвищити швидкодію магістралі. Іноді в магістралях застосовується часткове мультиплексування, тобто частина розрядів даних передається по немультиплексованих лініях, а інша частина - по мультиплексованих з адресою лініям.

Шина управління - це допоміжна шина, управляючі сигнали на якій визначають тип поточного циклу і фіксують моменти часу, відповідні різним частинам або стадіям циклу. Крім того, управляючі сигнали забезпечують узгодження роботи процесора (або іншого господаря магістралі, задатчика, master) з роботою пам'яті або пристрою вводу/виводу (пристрою-виконавця, slave). Управляючі сигнали також обслуговують запит і надання переривань, запит і надання прямого доступу.

Сигнали шини управління можуть передаватися як в позитивній логіці (рідше), так і в негативній логіці (частіше). Лінії шини управління можуть бути як однонаправленими, так і двонаправленими. Типи вихідних каскадів можуть бути самими різними: з двома станами (для однонаправлених ліній), з трьома станами (для двонаправлених ліній), з відкритим колектором (для двонаправлених і мультиплексованих ліній).

Найголовніші управляючі сигнали - це строби обміну, тобто сигнали, сформовані процесором і визначаючі моменти часу, в які проводиться пересилка даних по шині даних, обмін даними. Частіше всього в магістралі використовуються два різні строби обміну:

- Строб запису (виводу), який визначає момент часу, коли пристрій-виконавець може приймати дані, виставлені процесором на шину даних;

- Строб читання (вводу), який визначає момент часу, коли пристрій-виконавець повинен видати на шину даних код даних, який буде прочитаний процесором.

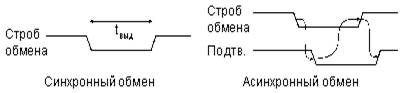

При цьому велике значення має те, як процесор закінчує обмін в межах циклу, в який момент він знімає свій строб обміну. Можливі два шляхи рішення (мал. 2.2):

При синхронному обміні процесор закінчує обмін даними самостійно, через раз і назавжди встановлений часовий інтервал витримки (tвит), тобто без урахування інтересів пристрою-виконавця;

При асинхронному обміні процесор закінчує обмін тільки тоді, коли пристрій-виконавець підтверджує виконання операції спеціальним сигналом.

Мал. 2.2. Синхронний обмін і асинхронний обмін.

Достоїнства синхронного обміну - більш простий протокол обміну, менша кількість управляючих сигналів.

Недоліки - відсутність гарантії, що виконавець виконав необхідну операцію, а також високі вимоги до швидкодії виконавця.

Достоїнства асинхронного обміну - більш надійна пересилка даних, можливість роботи з самими різними по швидкодії виконавцями.

Недолік - необхідність формування сигналу підтвердження всіма виконавцями, тобто додаткові апаратурні витрати.

Який тип обміну швидший? Відповідь на це питання неоднозначна. З одного боку, при асинхронному обміні потрібен якийсь час на вироблення, передачу додаткового сигналу і на його обробку процесором. З другого боку, при синхронному обміні доводиться штучно збільшувати тривалість строба обміну для відповідності вимогам більшого числа виконавців, щоб вони встигали обмінюватися інформацією в темпі процесора. Тому іноді в магістралі передбачають можливість як синхронного, так і асинхронного обміну, причому синхронний обмін є основним і досить швидким, а асинхронний застосовується тільки для повільних виконавців.

По типу обміну магістралі мікропроцесорних систем, що використовується, також діляться на синхронні і асинхронні.